## COMPUTER ENGINEERING DEPARTMENT

## **ICS 233**

## COMPUTER ARCHITECTURE & ASSEMBLY LANGUAGE

## **Final Exam**

First Semester (141)

Time: 8:00-10:30 AM

| Student Name | e: |  |  |  |

|--------------|----|--|--|--|

|              |    |  |  |  |

| Student ID.  | :  |  |  |  |

| Question | Max Points | Score |

|----------|------------|-------|

| Q1       | 20         |       |

| Q2       | 20         |       |

| Q3       | 26         |       |

| Q4       | 20         |       |

| Total    | 86         |       |

Dr. Aiman El-Maleh Dr. Samer Arafat

[20 Points]

(Q1)

(i) (10 points) Suppose that you have a processor that executes a certain program with the following

characteristics: 50% of the execution time is taken by multiply, 20% of the execution time is taken by divide, and the remaining 30% of the execution time is taken by other instructions.

We want the program to run faster. Suppose that we can improve the multiply to run 2 times faster and the divide to run 4 times faster. However, due to hardware cost, only one improvement can be made.

- 1. Which improvement should be done (multiply or divide?), assuming that the hardware cost is identical. Justify your answer. (4 points)

- 2. Given that the program executes on the processor without improvement in 10s, what will be the execution time of the program with the chosen improvement? (2 points)

- 3. Suppose we can now improve both the multiply and divide instructions. What is the speedup of the improved machine relative to the original machine? (4 points)

(ii) (3 points)

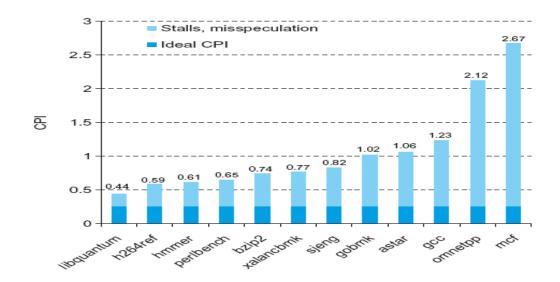

A certain Intel i7 processor has been tested using SPEC2013, which uses 12 benchmark software programs. The program names are listed on the X-axis of the following figure, below, and the corresponding CPI was computed and shown on the Y-axis. The numbers on top of each bar show the CPI that includes stalls and misprediction (called missspeculation in the graph). The ideal CPI = 0.25 for all benchmark software programs. What is the processor CPI, according to SPEC2013?

(iii) (7 points)

Given a certain processor that has the following operation times for processor components: instruction and data memories: 150 ps, ALU and adders: 140 ps, decode and register file access (read or write): 100 ps, which of the following would be faster and by how much, a single-cycle implementation for all instructions, or a multi-cycle implementation optimized for every class of instructions.

Assume the following instruction mix: 50% ALU, 10% Loads, 10% stores, 15% branches and 15% jumps. Ignore the delays in PC, mux, extender, and wires.

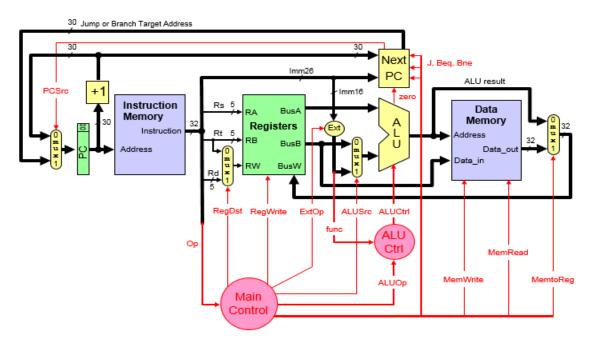

Consider the single-cycle CPU design given below.

You are required to complete the single cycle processor main control unit design.

1. Complete the main control signal values in the table below (6 points).

| Op   | Reg<br>Dst | Reg<br>Write | Ext<br>Op | ALU<br>Src | ALU<br>Op | Beq | Bne | J | Mem<br>Read | Mem<br>Write | Mem<br>toReg |

|------|------------|--------------|-----------|------------|-----------|-----|-----|---|-------------|--------------|--------------|

| R-   | DSt        | vviite       | Ор        | Sic        | Ор        |     |     |   | Keau        | vviite       | toKeg        |

| type |            |              |           |            |           |     |     |   |             |              |              |

| addi |            |              |           |            |           |     |     |   |             |              |              |

| slti |            |              |           |            |           |     |     |   |             |              |              |

| andi |            |              |           |            |           |     |     |   |             |              |              |

| ori  |            |              |           |            |           |     |     |   |             |              |              |

| xori |            |              |           |            |           |     |     |   |             |              |              |

| lw   |            |              |           |            |           |     |     |   |             |              |              |

| sw   |            |              |           |            |           |     |     |   |             |              |              |

| beq  |            |              |           |            |           |     |     |   |             |              |              |

| bne  |            |              |           |            |           |     |     |   |             |              |              |

| j    |            |              |           |            |           |     |     |   |             |              |              |

2. Derive the logic design of the control unit for all the control signals given in the table above, based on the given instructions, except ALUOp. Assume that the opcode of these instructions is a 6-bit opcode such that the opcode for R-type instructions is 0, the opcode for addi is 1, the opcode for slti is 2, and so on for the rest of the instructions. (7 points)

(ii) (7 points)

Modify the given single cycle datapath so that it implements the Jump and link instruction, jal. Draw only the blocks (resources) that must be modified. If the NextPC block needs to be changed, show its internal design details.

| Inst | truction | Meaning         | Format     |                   |  |  |

|------|----------|-----------------|------------|-------------------|--|--|

| jal  | label    | \$31=PC+4, jump | $op^6 = 3$ | imm <sup>26</sup> |  |  |

(Q3)

**(i)**

| Fil | ll the blank in each of the followi                                                      | ng c  | ques  | tions  | s: ( <b>7</b> | Poi   | nts)  |                       |

|-----|------------------------------------------------------------------------------------------|-------|-------|--------|---------------|-------|-------|-----------------------|

| 1.  | For a 20-stage pipeline, the maximum is                                                  | spee  | edup  | that o | can b         | e ach | ieved | over serial execution |

| 2.  | In a pipelined CPU design, structural                                                    | haza  | rds m | nay o  | ccur          | due t | 0     |                       |

| 3.  | In the MIPS 5-stage pipeline, data haz                                                   | zards | that  | may    | occu          | r are |       | hazards.              |

| 4.  | Hazards due to jump and branch instr                                                     | uctio | ns ar | e call | led _         |       |       | hazards.              |

| 5.  | In order to achieve a zero delay for a in th                                             | , .   |       |        | n bra         | nch,  | we ne | ed to use             |

| 6.  | Given the branch outcomes of a branch accuracy of prediction using a <b>2-bit p</b> ———. |       |       |        |               |       |       |                       |

|     | Branch Outcome                                                                           | N     | Т     | N      | N             | N     | Т     |                       |

|     | Branch Prediction                                                                        |       |       |        |               |       |       |                       |

(ii) Consider the single-cycle CPU design given in Q2, show the necessary modifications in the data path and control unit to implement this CPU as a 5-stage Pipeline without considering any type of hazards. Label all the added parts clearly. (7 Points)

(iii) Consider the following MIPS assembly language code:

```

I1: ADDI $a1, $0, 10

I2: LW $t2, 0($t5)

I3: ADD $t3, $t2, $t2

I4: SW $t3, 0($t5)

I5: ADDI $a1, $a1, -1

I6: ADDI $t5, $t5, 4

I7: BNE $a1, $0, I2

```

a. Complete the following table showing the timing of the above code on a 5-stage pipeline (IF, ID, EX, MEM, WB) that supports **forwarding**. Draw an arrow showing forwarding between the stage that provides the data and the stage that receives the data. Show all stall cycles (draw an X in the box). Assume that the branch delay is 1 clock cycle. **(9 Points)**

|          | 1  | 2  | 3  | 4 | 5  | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 |

|----------|----|----|----|---|----|---|---|---|---|----|----|----|----|----|----|----|----|----|

| I1: ADDI | IF | ID | EX |   | WB |   |   |   |   |    |    |    |    |    |    |    |    |    |

| I2: LW   |    |    |    |   |    |   |   |   |   |    |    |    |    |    |    |    |    |    |

| I3: ADD  |    |    |    |   |    |   |   |   |   |    |    |    |    |    |    |    |    |    |

| I4: SW   |    |    |    |   |    |   |   |   |   |    |    |    |    |    |    |    |    |    |

| I5: ADDI |    |    |    |   |    |   |   |   |   |    |    |    |    |    |    |    |    |    |

| I6: ADDI |    |    |    |   |    |   |   |   |   |    |    |    |    |    |    |    |    |    |

| I7: BNE  |    |    |    |   |    |   |   |   |   |    |    |    |    |    |    |    |    |    |

| 12: LW   |    |    |    |   |    |   |   |   |   |    |    |    |    |    |    |    |    |    |

| I3: ADD  |    |    |    |   |    |   |   |   |   |    |    |    |    |    |    |    |    |    |

b. Assume that branch instructions are implemented using a 1-cycle delayed branch. Rearrange the given code to reduce the number of stall cycles. Justify your solution? (3 Points)

| ( | ( | ) | 4 |    |

|---|---|---|---|----|

| 1 | • | , | _ | ., |

|       | 1. Using a larger block size in cache memory reduces misses while increases                                                                                                                                                                                                                                                                                                                                                              |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | misses.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       | 2. Increasing cache size reduces misses and misses.                                                                                                                                                                                                                                                                                                                                                                                      |

|       | 3. Small cache size is used for L1 caches to reduce                                                                                                                                                                                                                                                                                                                                                                                      |

|       | 4. Multi-level caches are used to reduce                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | 5. Valid and Modified bits are required for write policy.                                                                                                                                                                                                                                                                                                                                                                                |

| (ii)  | Assume that you have a 32-bit address and a cache with <b>8K byte data size</b> (not including tag and valid bits).                                                                                                                                                                                                                                                                                                                      |

| a.    | Assuming that the cache is organized as <b>direct-mapped</b> with a <b>16-byte block size</b> , determine the number of bits in the <u>offset</u> , <u>index</u> and <u>tag</u> fields. ( <b>3 Points</b> )                                                                                                                                                                                                                              |

| b.    | Assuming that the cache is organized as <b>four-way set associative</b> with a <b>16-byte block size</b> , determine the number of bits in the <u>offset</u> , <u>index</u> and <u>tag</u> fields. (3 Points)                                                                                                                                                                                                                            |

| (iii) | A processor runs at 2.5 GHz and has a CPI=1.6 for a perfect cache (i.e. without including the stall cycles due to cache misses). Assume that load and store instructions are 18% of the instructions. The processor has an I-cache with a 4% miss rate and a D-cache with 5% miss rate. The hit time is 1 clock cycle. Assume that the time required to transfer a block of data from the RAM to the cache, i.e. miss penalty, is 31 ns. |

| a.    | What is the number of stall cycles per instruction and the overall CPI? (4                                                                                                                                                                                                                                                                                                                                                               |

b. What is the average memory access time (AMAT) in ns? (3 Points)